# **MXI**<sup>™</sup>

# Getting Started with Your VXI/VME-PCI8026 and the NI-VXI<sup>™</sup>/NI-VISA<sup>™</sup> Software for Linux

December 1999 Edition Part Number 322651A-01

#### Worldwide Technical Support and Product Information

www.ni.com

#### **National Instruments Corporate Headquarters**

11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 794 0100

#### **Worldwide Offices**

Australia 03 9879 5166, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Brazil 011 284 5011, Canada (Calgary) 403 274 9391, Canada (Ontario) 905 785 0085, Canada (Québec) 514 694 8521, China 0755 3904939, Denmark 45 76 26 00, Finland 09 725 725 11, France 01 48 14 24 24, Germany 089 741 31 30, Greece 30 1 42 96 427, Hong Kong 2645 3186, India 91805275406, Israel 03 6120092, Italy 02 413091, Japan 03 5472 2970, Korea 02 596 7456, Mexico (D.F.) 5 280 7625, Mexico (Monterrey) 8 357 7695, Netherlands 0348 433466, Norway 32 27 73 00, Poland 48 22 528 94 06, Portugal 351 1 726 9011, Singapore 2265886, Spain 91 640 0085, Sweden 08 587 895 00, Switzerland 056 200 51 51, Taiwan 02 2377 1200, United Kingdom 01635 523545

For further support information, see the *Technical Support Resources* appendix. To comment on the documentation, send e-mail to techpubs@ni.com

© Copyright 1999 National Instruments Corporation. All rights reserved.

# **Important Information**

#### Warranty

The National Instruments MXIbus boards and accessories are warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this document is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

#### Trademarks

LabVIEW<sup>TM</sup>, National Instruments<sup>TM</sup>, ni.com<sup>TM</sup>, NI-VISA<sup>TM</sup>, NI-VXI<sup>TM</sup>, and VXIpc<sup>TM</sup> are trademarks of National Instruments Corporation.

Product and company names mentioned herein are trademarks or trade names of their respective companies.

#### WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

(1) NATIONAL INSTRUMENTS PRODUCTS ARE NOT DESIGNED WITH COMPONENTS AND TESTING FOR A LEVEL OF RELIABILITY SUITABLE FOR USE IN OR IN CONNECTION WITH SURGICAL IMPLANTS OR AS CRITICAL COMPONENTS IN ANY LIFE SUPPORT SYSTEMS WHOSE FAILURE TO PERFORM CAN REASONABLY BE EXPECTED TO CAUSE SIGNIFICANT INJURY TO A HUMAN.

(2) IN ANY APPLICATION, INCLUDING THE ABOVE, RELIABILITY OF OPERATION OF THE SOFTWARE PRODUCTS CÁN BE IMPAIRED BY ADVERSE FACTORS, INCLUDING BUT NOT LIMITED TO FLUCTUATIONS IN ELECTRICAL POWER SUPPLY, COMPUTER HARDWARE MALFUNCTIONS, COMPUTER OPERATING SYSTEM SOFTWARE FITNESS, FITNESS OF COMPILERS AND DEVELOPMENT SOFTWARE USED TO DEVELOP AN APPLICATION, INSTALLATION ERRORS, SOFTWARE AND HARDWARE COMPATIBILITY PROBLEMS, MALFUNCTIONS OR FAILURES OF ELECTRONIC MONITORING OR CONTROL DEVICES, TRANSIENT FAILURES OF ELECTRONIC SYSTEMS (HARDWARE AND/OR SOFTWARE), UNANTICIPATED USES OR MISUSES, OR ERRORS ON THE PART OF THE USER OR APPLICATIONS DESIGNER (ADVERSE FACTORS SUCH AS THESE ARE HEREAFTER COLLECTIVELY TERMED "SYSTEM FAILURES"). ANY APPLICATION WHERE A SYSTEM FAILURE WOULD CREATE A RISK OF HARM TO PROPERTY OR PERSONS (INCLUDING THE RISK OF BODILY INJURY AND DEATH) SHOULD NOT BE RELIANT SOLELY UPON ONE FORM OF ELECTRONIC SYSTEM DUE TO THE RISK OF SYSTEM FAILURE. TO AVOID DAMAGE, INJURY, OR DEATH, THE USER OR APPLICATION DESIGNER MUST TAKE REASONABLY PRUDENT STEPS TO PROTECT AGAINST SYSTEM FAILURES, INCLUDING BUT NOT LIMITED TO BACK-UP OR SHUT DOWN MECHANISMS. BECAUSE EACH END-USER SYSTEM IS CUSTOMIZED AND DIFFERS FROM NATIONAL INSTRUMENTS' TESTING PLATFORMS AND BECAUSE A USER OR APPLICATION DESIGNER MAY USE NATIONAL INSTRUMENTS PRODUCTS IN COMBINATION WITH OTHER PRODUCTS IN A MANNER NOT EVALUATED OR CONTEMPLATED BY NATIONAL INSTRUMENTS, THE USER OR APPLICATION DESIGNER IS ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY OF NATIONAL INSTRUMENTS PRODUCTS WHENEVER NATIONAL INSTRUMENTS PRODUCTS ARE INCORPORATED IN A SYSTEM OR APPLICATION, INCLUDING, WITHOUT LIMITATION, THE APPROPRIATE DESIGN, PROCESS AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

# **Compliance** FCC/Canada Radio Frequency Interference Compliance\*

#### **Determining FCC Class**

The Federal Communications Commission (FCC) has rules to protect wireless communications from interference. The FCC places digital electronics into two classes. These classes are known as Class A (for use in industrial-commercial locations only) or Class B (for use in residential or commercial locations). Depending on where it is operated, this product could be subject to restrictions in the FCC rules. (In Canada, the Department of Communications (DOC), of Industry Canada, regulates wireless interference in much the same way.)

Digital electronics emit weak signals during normal operation that can affect radio, television, or other wireless products. By examining the product you purchased, you can determine the FCC Class and therefore which of the two FCC/DOC Warnings apply in the following sections. (Some products may not be labelled at all for FCC, if so the reader should then assume these are Class A devices.)

FCC Class A products only display a simple warning statement of one paragraph in length regarding interference and undesired operation. Most of our products are FCC Class A. The FCC rules have restrictions regarding the locations where FCC Class A products can be operated.

FCC Class B products display either a FCC ID code, starting with the letters **EXN**, or the FCC Class B compliance mark that appears as shown here on the right.

The curious reader can consult the FCC web site http://www.fcc.gov for more information.

#### **FCC/DOC Warnings**

This equipment generates and uses radio frequency energy and, if not installed and used in strict accordance with the instructions in this manual and the CE Mark Declaration of Conformity\*\*, may cause interference to radio and television reception. Classification requirements are the same for the Federal Communications Commission (FCC) and the Canadian Department of Communications (DOC).

Changes or modifications not expressly approved by National Instruments could void the user's authority to operate the equipment under the FCC Rules.

#### **Class A**

#### **Federal Communications Commission**

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

#### **Canadian Department of Communications**

This Class A digital apparatus meets all requirements of the Canadian Interference-Causing Equipment Regulations.

Cet appareil numérique de la classe A respecte toutes les exigences du Règlement sur le matériel brouilleur du Canada.

#### **Class B**

#### **Federal Communications Commission**

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful

interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- · Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- · Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

#### **Canadian Department of Communications**

This Class B digital apparatus meets all requirements of the Canadian Interference-Causing Equipment Regulations.

Cet appareil numérique de la classe B respecte toutes les exigences du Règlement sur le matériel brouilleur du Canada.

#### **European Union - Compliance to EEC Directives**

Readers in the EU/EEC/EEA must refer to the Manufacturer's Declaration of Conformity (DoC) for information\*\* pertaining to the CE Mark compliance scheme. The Manufacturer includes a DoC for most every hardware product except for those bought for OEMs, if also available from an original manufacturer that also markets in the EU, or where compliance is not required as for electrically benign apparatus or cables.

- \* Certain exemptions may apply in the USA, see FCC Rules §15.103 **Exempted devices**, and §15.105(c). Also available in sections of CFR 47.

- \*\* The CE Mark Declaration of Conformity will contain important supplementary information and instructions for the user or installer.

#### **About This Manual**

| How To Use the Manual Set | . xiii |

|---------------------------|--------|

| Conventions               | .xiv   |

| Related Documentation     | .xv    |

#### Chapter 1 Introduction and Quick Start

| How to Use This Manual                                    | 1-2 |

|-----------------------------------------------------------|-----|

| VXI/VME-PCI8026 Kit Overview                              |     |

| What You Need to Get Started                              |     |

| MXI-2 Description                                         |     |

| Hardware Description                                      |     |

|                                                           |     |

| Software Description                                      | 1-5 |

| Optional Software                                         | 1-0 |

| Quick Start                                               |     |

| Hardware Installation                                     | 1-7 |

| Installing and Loading the NI-VXI/VISA Software for Linux | 1-8 |

| VME Users                                                 | 1-8 |

| Device Interaction                                        | 1-8 |

| Default Settings                                          |     |

| PCI-MXI-2                                                 |     |

| VXI/VME-MXI-2                                             |     |

### Chapter 2 PCI-MXI-2 Configuration and Installation

| Configure the PCI-MXI-2 | 2-1 |

|-------------------------|-----|

| Configuration EEPROM    |     |

| Onboard DRAM            |     |

| Install the PCI-MXI-2   | 2-3 |

## Chapter 3 VXI-MXI-2 Configuration and Installation

| Configure the VXI-MXI-2      | 3-1 |

|------------------------------|-----|

| Front Panel Features         | 3-3 |

| Removing the Metal Enclosure |     |

| VXIbus Logical Address       | 3-3 |

| VXIbus Slot 0/Non-Slot 0     |     |

| VXIbus Local Bus          | 3-7  |

|---------------------------|------|

| VXIbus CLK10 Routing      |      |

| Trigger Input Termination | 3-12 |

| MXIbus Termination        |      |

| Configuration EEPROM      | 3-15 |

| Onboard DRAM              | 3-17 |

| Install the VXI-MXI-2     | 3-18 |

| Connect the MXIbus Cable  | 3-19 |

## Chapter 4 VME-MXI-2 Configuration and Installation

| Configure the VME-MXI-2         | 4-1  |

|---------------------------------|------|

| Front Panel Features            |      |

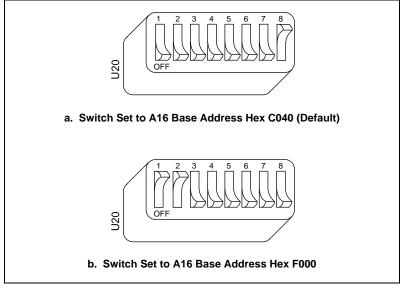

| VMEbus A16 Base Address         | 4-3  |

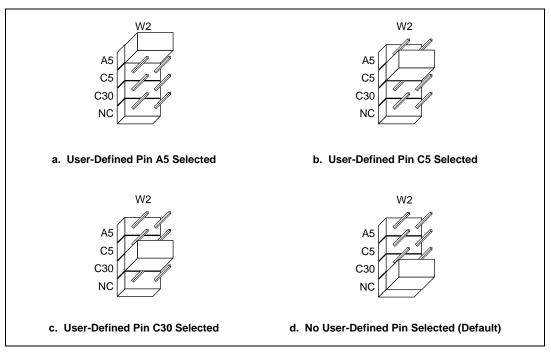

| VME-MXI-2 Intermodule Signaling | 4-4  |

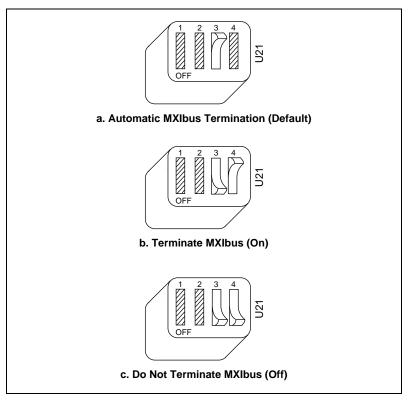

| MXIbus Termination              | 4-5  |

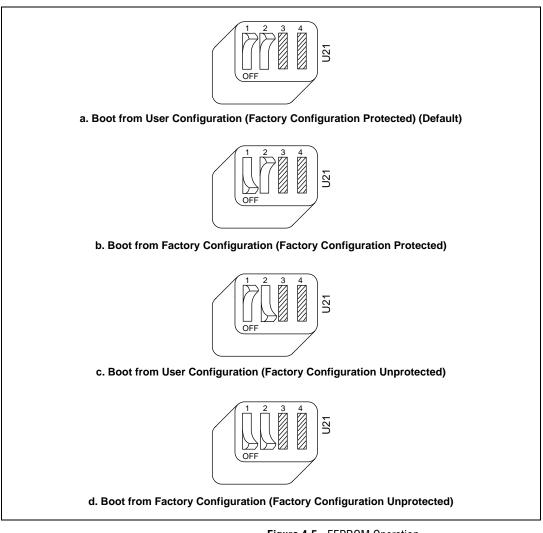

| Configuration EEPROM            | 4-7  |

| Onboard DRAM                    | 4-8  |

| Install the VME-MXI-2           | 4-10 |

| Connect the MXIbus Cable        | 4-11 |

#### Chapter 5 NI-VXI/VISA Software Installation

| Installing the NI-VXI/VISA Software for Linux | 5-1 |

|-----------------------------------------------|-----|

| Removing the NI-VXI Driver for Linux          | 5-2 |

| Using the NI-VXI/VISA Software                | 5-2 |

| Completing the Software Installation          | 5-3 |

## Chapter 6 NI-VXI Configuration Utility

| Running the VXItedit Configuration Utility | 6-1 |

|--------------------------------------------|-----|

| PCI-MXI-2 Configuration Editor             | 6-2 |

| Update Current Configuration               | 6-2 |

| Record Configuration to File               | 6-2 |

| Load Configuration from File               | 6-2 |

| Revert to Current Configuration            | 6-3 |

| Logical Address Configuration Editor       | 6-3 |

| Device Settings                            | 6-3 |

| Logical Address                            | 6-3 |

| Device Type                                | 6-3 |

| Address Space                              | 6-4 |

| VXI/VME Shared Memory              | 6-4  |

|------------------------------------|------|

| Resource Manager                   | 6-4  |

| Resource Manager Delay             | 6-4  |

| Device Configuration Editor        | 6-5  |

| Default Controller (LA –1)         | 6-5  |

| System IRQ Level                   |      |

| Servant Area Size                  | 6-5  |

| Number of Handlers                 |      |

| Number of Interrupters             |      |

| Protocol Register                  |      |

| Read Protocol Response             |      |

| Bus Configuration Editor           |      |

| MXI Bus                            |      |

| MXI System Controller              |      |

| MXI Bus Timeout                    |      |

| MXI CLK10                          | 6-8  |

| MXI Transfer Limit                 |      |

| MXI-2 Auto Retry                   |      |

| A24/A32 Write Posting              | 6-9  |

| PCI Bus                            |      |

| User Window and Driver Window      |      |

| Expansion ROM                      |      |

| VXI/VME-MXI-2 Configuration Editor |      |

| LA Selection and Logical Address   |      |

| Address Space and Requested Memory |      |

| A16 and A24/A32 Write Posting      |      |

| Interlocked Mode                   |      |

| VXI/VME Bus Options                |      |

| VMEbus System Controller           |      |

| VXI/VME Bus Timeout Value          |      |

| VXI/VME Auto Retry                 |      |

| Transfer Limit                     |      |

| Arbiter Type                       |      |

| Request Level                      |      |

| VXI/VME Fair Requester             |      |

| Arbiter Timeout                    |      |

| MXI Bus Options                    |      |

| MXI Bus System Controller          |      |

| MXI Bus Timeout Value              |      |

| Advanced MXI Settings              |      |

| MXI Auto Retry                     |      |

| Transfer Limit                     |      |

| Parity Checking                    | 6-18 |

| MXI Fair Requester  | 18 |

|---------------------|----|

| MXI CLK10 Signal6-1 | 19 |

## Chapter 7 Using the NI-VXI/VISA Software

| Interactive Control of NI-VXI/VISA                        |  |

|-----------------------------------------------------------|--|

| Example Programs                                          |  |

| Programming Considerations                                |  |

| Multiple Applications Using the NI-VXI and VISA Libraries |  |

| Low-Level Access Functions                                |  |

| Local Resource Access Functions                           |  |

| System Configuration Functions                            |  |

| Compiling Your C Program for NI-VXI/VISA                  |  |

| Symbols                                                   |  |

| -                                                         |  |

## Appendix A Specifications

| PCI-MXI-2                          |

|------------------------------------|

| MXIbus Capability DescriptionsA-1  |

| PCI Functionality A-2              |

| Requirements A-2                   |

| Environmental                      |

| Physical A-3                       |

| Electrical A-3                     |

| Performance                        |

| VXI-MXI-2                          |

| MXIbus Capability Descriptions A-4 |

| VMEbus Capability Codes            |

| Requirements                       |

| Environmental                      |

| Physical A-6                       |

| Electrical A-6                     |

| Performance                        |

| VME-MXI-2                          |

| MXIbus Capability Descriptions A-8 |

| VMEbus Capability Codes A-8        |

| Requirements A-10                  |

| Environmental                      |

| Physical A-10                      |

| Electrical A-10                    |

| Performance A-11                   |

## Appendix B NI-VXI/VISA Software Overview

| Main Programs and Files  | B-1 |

|--------------------------|-----|

| Header Files for NI-VXI  | B-1 |

| Header Files for NI-VISA | B-2 |

## Appendix C EEPROM Configuration

| -                         |               |     |

|---------------------------|---------------|-----|

| Controlling the EEPROM Op | peration      | C-1 |

| Fixing an Invalid EEPROM  | Configuration | C-2 |

### Appendix D Common Questions

### Appendix E Technical Support Resources

## Glossary

## Index

## Figures

| Figure 2-1.  | PCI-MXI-2 Parts Locator Diagram   | 2-2  |

|--------------|-----------------------------------|------|

| Figure 2-2.  | PCI-MXI-2 Installed in a Computer |      |

|              |                                   |      |

| Figure 3-1.  | VXI-MXI-2 Right-Side Cover        |      |

| Figure 3-2.  | Logical Address Selection         |      |

| Figure 3-3.  | VXIbus Slot Configuration         |      |

| Figure 3-4.  | VXIbus Local Bus Configuration    |      |

| Figure 3-5.  | VXIbus CLK10 Routing              |      |

| Figure 3-6.  | SMB CLK10 Settings                |      |

| Figure 3-7.  | Receiving or Driving MXIbus CLK10 |      |

| Figure 3-8.  | SMB Trigger Input Termination     | 3-13 |

| Figure 3-9.  | MXIbus Termination                |      |

| Figure 3-10. | EEPROM Operation                  | 3-16 |

| Figure 3-11. | SIMM Size Configuration           |      |

| Figure 3-12. | MXI-2 Cable Configuration Using   |      |

|              | a PCI-MXI-2 and a VXI-MXI-2       |      |

| Figure 4-1. | VME-MXI-2 Parts Locator Diagram          | 4-2  |

|-------------|------------------------------------------|------|

| Figure 4-2. | Base Address Selection                   | 4-4  |

| Figure 4-3. | VME-MXI-2 Intermodule Signaling Settings | 4-5  |

| Figure 4-4. | MXIbus Termination                       | 4-6  |

| Figure 4-5. | EEPROM Operation                         | 4-8  |

| Figure 4-6. | SIMM Size Configuration                  | 4-9  |

| Figure 4-7. | MXI-2 Cable Configuration Using          |      |

|             | a PCI-MXI-2 and a VME-MXI-2              | 4-12 |

| Figure C-1. | EEPROM Operation Default Settings        | C-1  |

| Figure C-2. | Restoring the Factory Configuration      | C-2  |

### Tables

| Table 1-1. | PCI-MXI-2 Hardware Default Settings                    | 1-9  |

|------------|--------------------------------------------------------|------|

| Table 1-2. | PCI-MXI-2 Logical Address Configuration Editor         |      |

|            | Default Settings                                       | 1-10 |

| Table 1-3. | PCI-MXI-2 Device Configuration Editor Default Settings | 1-11 |

| Table 1-4. | PCI-MXI-2 Bus Configuration Editor Default Settings    | 1-11 |

| Table 1-5. | VXI-MXI-2 Hardware Default Settings                    | 1-12 |

| Table 1-6. | VME-MXI-2 Hardware Default Settings                    | 1-13 |

| Table 1-7. | VXI/VME-MXI-2 Configuration Editor Default Settings    | 1-13 |

| Table 2-1. | PCI-MXI-2 DRAM Configurations                          |      |

| Table 3-1. | VXI-MXI-2 DRAM Configurations                          | 3-17 |

| Table 4-1. | VME-MXI-2 DRAM Configurations                          | 4-9  |

This manual contains instructions for installing and configuring the National Instruments VXI-PCI8026 or VME-PCI8026 Series interface kit for Linux. The VXI-PCI8026 kit includes a VXI-MXI-2 module that plugs into a VXI mainframe and links your PCI-based computer to the VXIbus. The VME-PCI8026 kit includes a VME-MXI-2 that plugs into a VME chassis and links your PCI-based computer to the VMEbus. Both kits include the PCI-MXI-2 interface board, which links your computer to the MXIbus, and the NI-VXI bus interface software. The VXI-PCI8026 and VME-PCI8026 kits are fully VXI*plug&play* compliant.

This manual uses the term *VXI/VME-PCI8026* when information applies to either kit and the term *VXI/VME-MXI-2* when information applies to either the VXI-MXI-2 or the VME-MXI-2.

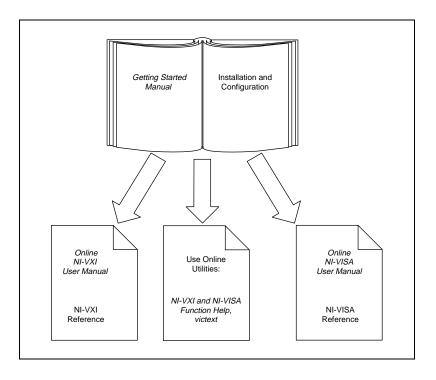

## How To Use the Manual Set

Begin by reading this getting started manual to guide you through the installation and configuration of the hardware and software. You should install and configure the components of the VXI/VME-PCI8026 kit in the order in which this manual describes them. Be sure to review the *Quick Start* and *Default Settings* sections in Chapter 1, *Introduction and Quick Start*. The material in those sections may be all you need to get up and running with your VXI/VME-PCI8026 kit.

When you have successfully set up your system, you can begin to develop applications in NI-VXI and/or NI-VISA. The *NI-VXI User Manual* presents the concepts of VXI and prepares you for detailed explanations of the NI-VXI functions. Study the descriptions of each function given in the online help utility to fully understand the purpose and syntax of each function. This manual is available in the *NIVXI*/manuals directory (where *NIVXI* refers to the actual location where you have installed the NI-VXI software). Use the Acrobat Reader program, Version 3 or later, to open this file.

We recommend the VISA API for new applications. Refer to the *NI-VISA User Manual* to learn about VISA and how to use it in your system. The NI-VISA online help describes the attributes, events, and operations you can use in NI-VISA. The user manual is available in the *VXIpnp*/linux/NIvisa/manuals directory (where *VXIpnp* refers to the actual location where you have installed the NI-VISA software). Use the Acrobat Reader program, Version 3 or later, to open this file.

# Conventions

|          | The following conventions are used in this manual:                                                                                                                 |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| •        | The ♦ symbol indicates that the following text applies only to a specific product, a specific operating system, or a specific software version.                    |  |  |

|          | This icon denotes a note, which alerts you to important information.                                                                                               |  |  |

| Â        | This icon denotes a caution, which advises you of precautions to take to avoid injury, data loss, or a system crash.                                               |  |  |

| <u> </u> | This icon denotes a warning, which advises you of precautions to take to avoid being electrically shocked.                                                         |  |  |

| bold     | Bold text denotes items that you must select or click on in the software,<br>such as menu items and dialog box options. Bold text also denotes<br>parameter names. |  |  |

| italic           | Italic text denotes variables, emphasis, a cross reference, or an introduction<br>to a key concept. This font also denotes text that is a placeholder for a word<br>or value that you must supply.                                                                                                                                                                  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| monospace        | Text in this font denotes text or characters that you should enter from the keyboard, sections of code, programming examples, and syntax examples. This font is also used for the proper names of disk drives, paths, directories, programs, subprograms, subroutines, device names, functions, operations, variables, filenames and extensions, and code excerpts. |  |

| monospace bold   | Bold text in this font denotes the messages and responses that the computer<br>automatically prints to the screen. This font also emphasizes lines of code<br>that are different from the other examples.                                                                                                                                                           |  |

| monospace italic | Italic text in this font denotes text that is a placeholder for a word or value that you must supply. Usually this is a variable in a directory path; for example, <i>NIVXI</i> refers to the actual location where you have installed the NI-VXI software.                                                                                                         |  |

## **Related Documentation**

The following documents contain information that you may find helpful as you read this manual:

- ANSI/IEEE Standard 1014-1987, IEEE Standard for a Versatile Backplane Bus: VMEbus

- ANSI/IEEE Standard 1155-1993, IEEE VMEbus Extensions for Instrumentation: VXIbus

- ANSI/VITA 1-1994, VME64

- *Multisystem Extension Interface Bus Specification*, Version 2.0, National Instruments Corporation

- PCI Local Bus Specification, Revision 2.0, PCI Special Interest Group

- VXI-MXI-2 User Manual, National Instruments Corporation

- VME-MXI-2 User Manual, National Instruments Corporation

- VXI-6, *VXIbus Mainframe Extender Specification*, Rev. 2.0, VXIbus Consortium

# **Introduction and Quick Start**

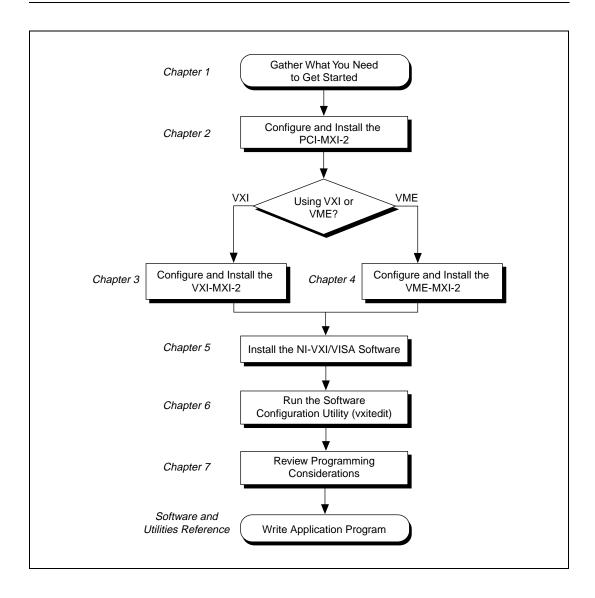

This chapter describes the VXI/VME-PCI8026 interface kits, lists what you need to get started, introduces the concepts of MXI-2, and includes a brief description of the hardware and software.

This chapter also contains a *Quick Start* section, which has the basic information you need to install the VXI/VME-PCI8026 interface kit with a simple configuration, along with a *Default Settings* section, which lists the hardware and software default settings for easy reference. You may find that these sections contain as much information as you need to get started with your VXI/VME-PCI8026 interface kit.

This manual uses the term *VXI/VME-PCI8026* when information applies to either the VXI-PCI8026 kit, which contains a VXI-MXI-2 module, or the VME-PCI8026 kit, which contains a VME-MXI-2 module. Similarly, the term *VXI/VME-MXI-2* means that information applies to either the VXI-MXI-2 or the VME-MXI-2.

The following flowchart shows where to turn in this manual for more details on configuring and using the hardware and software.

# How to Use This Manual

# VXI/VME-PCI8026 Kit Overview

The VXI/VME-PCI8026 interface kits link any computer with a PCI bus (hereafter referred to as a PCI-based computer) directly to the VXIbus or VMEbus using the high-speed Multisystem eXtension Interface bus (MXI-2).

A PCI-based computer equipped with a VXI-PCI8026 interface can function as a VXI Commander and Resource Manager. A PCI-based computer equipped with a VME-PCI8026 can function as a VMEbus master and/or slave device. The VXI/VME-PCI8026 makes your PCI-based computer behave as if it were plugged directly into the VXI/VME backplane as an embedded CPU VXI/VME module.

The software included with the kits is for Intel *x*86-based computers.

# What You Need to Get Started

- $\Box$  A PCI-based computer running Linux kernel 2.2.*x*

- □ VXIbus or VMEbus mainframe

- □ PCI-MXI-2 interface board

- □ VXI-MXI-2 or VME-MXI-2 interface module

- MXI-2 cable

- □ NI-VXI/VISA software media for the PCI-MXI-2

## **MXI-2** Description

MXI-2 is the second generation of the National Instruments MXIbus product line. The MXIbus is a general-purpose, 32-bit, multimaster system bus on a cable. MXI-2 expands the number of signals on a standard MXI cable by including VXI triggers, all VXI interrupts, CLK10, and all of the utility bus signals (SYSFAIL\*, SYSRESET\*, and ACFAIL\*).

Because MXI-2 incorporates all of these new signals into a single connector, the triggers, interrupts, and utility signals can be extended not only to other mainframes but also to the local CPU in all MXI-2 products using a single cable. Thus, MXI-2 lets CPU interface boards such as the

PCI-MXI-2 perform as if they were plugged directly into the VXI/VME backplane.

In addition, MXI-2 boosts data throughput performance past previous-generation MXIbus products by defining new high-performance protocols. MXI-2 is a superset of MXI. All accesses initiated by MXI devices will work with MXI-2 devices. However, MXI-2 defines synchronous MXI block data transfers which surpass previous block data throughput benchmarks. The new synchronous MXI block protocol increases MXI-2 throughput to a maximum of 33 MB/s between two MXI-2 devices. All National Instruments MXI-2 boards can initiate and respond to synchronous MXI block cycles.

R

Note In the remainder of this manual, the term MXIbus refers to MXI-2.

## **Hardware Description**

The PCI-MXI-2 is a half-size, PCI-compatible plug-in circuit board that plugs into one of the expansion slots in your PCI-based computer. It links your PCI-based computer directly to the MXIbus and vice versa. Because the PCI-MXI-2 uses the same communication register set that other VXIbus message-based devices use, other MXIbus devices view the PCI-MXI-2 as a VXIbus device. The PCI-MXI-2 can also function as the MXIbus System Controller and can terminate the MXIbus signals directly on the PCI-MXI-2. In addition, you can have up to 16 MB of onboard DRAM on the PCI-MXI-2 that can be shared with the MXIbus and VXI/VMEbus and used as a dedicated data buffer.

The VXI-MXI-2 module is an extended-class, register-based VXIbus device with optional VXIbus Slot 0 capability so that it can reside in any slot in a C-size or D-size chassis.

**Note** D-size VXI mainframes have connections for a P3 connector. The VXI-MXI-2, however, does not have this connector and, if configured as a Slot 0 controller, cannot provide the necessary control for VXI devices that need P3 support.

The VXI-MXI-2 uses address mapping to convert MXIbus cycles into VXIbus cycles and vice versa. By connecting to the PCI-MXI-2 board, the VXI-MXI-2 links the PCI bus to the VXIbus. The VXI-MXI-2 can automatically determine whether it is located in VXI Slot 0 and/or if it is the MXIbus System Controller.

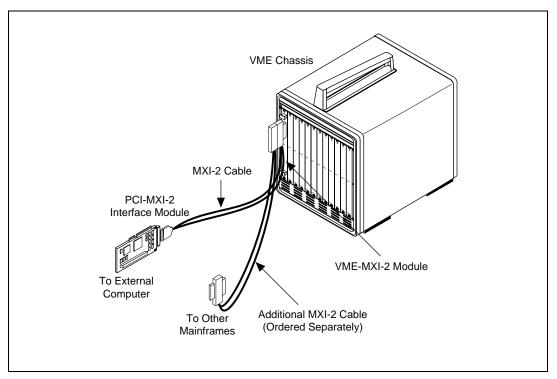

The VME-MXI-2 module is a single-slot, double-height VMEbus device with optional VMEbus System Controller functions. It uses address mapping to convert MXIbus cycles into VMEbus cycles and vice versa, just like the VXI-MXI-2. By connecting to the PCI-MXI-2 board, it links the PCI bus to the VMEbus. The VME-MXI-2 can automatically determine if it is located in the first slot of a VMEbus chassis and if it is the MXIbus System Controller.

Also, the VXI-MXI-2 and VME-MXI-2 automatically terminate the MXIbus if installed as the first or last device in the MXIbus. If installed in the middle of the MXIbus, both the VXI-MXI-2 and VME-MXI-2 automatically disable MXIbus termination. In addition, you can have up to 64 MB of onboard DRAM on the VXI-MXI-2 and VME-MXI-2 modules that can either be shared with the VXI/VMEbus and MXIbus or used as a dedicated data buffer.

The PCI-MXI-2, VXI-MXI-2, and VME-MXI-2 products achieve high-performance block transfer rates by integrating the MITE custom ASIC, a sophisticated dual-channel DMA controller with standard interfaces for VXI, VME, MXI, and PCI. By using MITE DMA to transfer data and commands to and from devices, the MITE frees up a computer's microprocessor to perform other tasks such as data analysis and presentation. In addition to DMA, the MITE incorporates both the new Synchronous MXI protocol and VME64 MBLT (8-byte block transfers in which both the address bus and data bus are used to transfer data) directly into the ASIC to perform the fastest transfer operation to instruments.

# **Software Description**

The NI-VXI/VISA bus interface software for the PCI-MXI-2 and Linux includes a Resource Manager, a text-based interactive VXI resource editor program, a comprehensive library of software routines for VXI/VME programming, and a text-based interactive control program for interacting with VXI/VME or VISA. You can use this software to seamlessly program multiple-mainframe configurations and have software compatibility across a variety of VXI/VME controller platforms.

NI-VISA has a comprehensive library of software routines not only for VXI/VME programming, but also for GPIB, GPIB-VXI, and serial. You can use this software to program instruments connected via different types of interfaces.

# **Optional Software**

Your VXI/VME-PCI8026 kit includes the NI-VXI/VISA bus interface software. In addition, you can use National Instruments LabVIEW to ease your programming task. This standardized program matches the modular virtual instrument capability of VXI and can reduce your VXI/VMEbus software development time.

LabVIEW is a complete programming environment that departs from the sequential nature of traditional programming languages and features a graphical programming environment.

# **Quick Start**

You can use this *Quick Start* section as a guide to quickly configure and operate your VXI or VME system using the PCI-MXI-2 and the VXI-MXI-2 or VME-MXI-2.

The *Quick Start* summary assumes that you intend to perform a basic configuration as follows:

- You have one PCI-MXI-2 interface module, which you will install in your 5 V PCI-based computer as the Resource Manager (logical address 0).

- You have either one C-size VXI-MXI-2 or one 6U, B-size VME-MXI-2, which you will install in a VXI or VME chassis, respectively, and connect to the PCI-MXI-2.

- You will be using the NI-VXI/VISA software for initialization, configuration, and device interaction.

- You will use the default hardware and software settings:

- The PCI-MXI-2 is the main controller, the VXI/VME Resource Manager, and a message-based device.

- Your system contains only one VXI or VME chassis.

- There is no shared memory used on the PCI-based computer, the PCI-MXI-2, or the VXI/VME-MXI-2.

Refer to the end of this chapter for a complete listing of the hardware and software default settings. If you need more information, or if you want to try a different configuration, refer to the appropriate hardware or software chapters in this manual, which describe the installation and configuration steps in greater detail.

#### **Hardware Installation**

To guard against electrostatic discharge, touch the antistatic plastic package to a metal part of your computer before removing the PCI-MXI-2 from the package. Install the PCI-MXI-2 in an available PCI slot in your PCI-based computer.

By default, the PCI-MXI-2 automatically detects whether it should be the system controller on the MXIbus. Verify that the correct cable end labeled *Connect This End To Device Closest To MXIbus Controller In This Daisy Chain* is attached securely to the PCI-MXI-2. You must connect the cable this way so that the PCI-MXI-2 can correctly detect whether it should be the system controller on the MXIbus. For more information, refer to Chapter 2, *PCI-MXI-2 Configuration and Installation*.

You received either a VXI-MXI-2 or a VME-MXI-2 in your VXI/VME-PCI8026 kit. To guard against electrostatic discharge, touch the antistatic plastic package to a metal part of your computer before removing the VXI-MXI-2 or VME-MXI-2 from the package. Install the VXI-MXI-2 in the first slot of a VXI chassis, or install the VME-MXI-2 in the first slot of a VME chassis.

The VXI/VME-MXI-2 default configuration automatically detects whether it should be the VXI/VMEbus system controller. The VXI/VMEbus system controllers operate certain VXI/VMEbus lines as required for VXI/VME systems. Verify that any other VXI/VME devices with system controller capability that are located in the same chassis are not configured as system controller. Having more than one device configured as system controller will damage the VXI/VME system.

For VXI systems that include VME devices, ensure that the VME devices are not configured in the upper 16 KB (starting from 0xC000) of the A16 address space. This region is reserved for VXI device configuration registers, which are used for initializing, configuring, and interacting with VXI devices. The PCI-MXI-2 and VME-MXI-2 also use this region for this purpose.

Also ensure that no VXI devices in your system are configured for either logical addresses 0 or 1. These are the default configurations for the PCI-MXI-2 and the VXI-MXI-2, respectively.

For more details on the VXI-MXI-2 or VME-MXI-2 hardware, refer to either Chapter 3, *VXI-MXI-2 Configuration and Installation*, or Chapter 4, *VME-MXI-2 Configuration and Installation*.

#### Installing and Loading the NI-VXI/VISA Software for Linux

For information on installing, uninstalling, or using the NI-VXI/VISA software, refer to Chapter 5, *NI-VXI/VISA Software Installation*.

#### **VME Users**

When used with a VXI-MXI-2, resman identifies and configures the VXI devices, including the VXI-MXI-2. When used with a VME-MXI-2, resman configures the VME-MXI-2 to allow the PCI-MXI-2 to access devices in the VME chassis. resman does not configure VME devices. The VME specification does not specify the initialization and configuration procedures that the VXI specification requires.

It is recommended that you enter the information about your VME devices into the vxitedit utility. resman can then properly configure the various device-specific VME address spaces and VME interrupt lines. For more information on configuring non-VXI devices in your VXI system, refer to the description of the *Non-VXI Device Configuration Editor* in Chapter 3, *VXI Text Resource Editor*, in the *NI-VXI Text Utilities Reference Manual*. For more details about installing the NI-VXI software, refer to Chapter 5, *NI-VXI/VISA Software Installation*, in this manual.

#### **Device Interaction**

After resman has detected and configured all VXI/VME devices, you can view specific information on each device in your system by using the vxitedit utility. These utilities include a **Resource Manager Display**, which contains a description for each device, including each VXI device's logical address.

You can interact with your VXI/VME devices by using the victext utility for NI-VXI. These utilities let you interactively control your VXI/VME devices without having to use a conventional programming language, LabVIEW, or LabWindows/CVI.

Try the following in victext:

At the prompt, type help vxiinreg

This help file shows you the syntax for this command, which reads VXI device configuration registers. The first argument is a logical address, and the second is the offset of the VXI device configuration register to be read.

Now type vxiinreg 1,0

This should return a value, such as:

Return Status (0): SUCCESS. value = 0x4ff6

If the value ends with ff6, you have successfully read the National Instruments manufacturer ID from the ID register for the VXI/VME-MXI-2.

You may now want to read the configuration registers from other VXI devices in your system using the command vxiinreg. This command accesses only the upper 16 KB of A16 space. Try reading the registers from one of the devices listed in the **Resource Manager Display** of vxitedit. In this way, you can verify that your PCI-MXI-2 can access each of the devices in your VXI system successfully.

You can also access VXI and VME devices that are configured in A16, A24, and A32 address space by using the vxiin or vxiout commands. For more information regarding victext operation and commands, refer to the online help.

# **Default Settings**

This section summarizes the hardware and software default settings for the VXI/VME-PCI8026 kit. If you need more information about a particular setting, or if you want to try a different configuration, please refer to the appropriate hardware or software chapters in this manual. The manual flowchart at the beginning of this chapter directs you to where to find the information you need.

### PCI-MXI-2

This section summarizes the hardware and software default settings for the PCI-MXI-2.

| Hardware Component | Default Setting                                                  |

|--------------------|------------------------------------------------------------------|

| U17 Switch 1 (FOV) | OFF: PCI-MXI-2 boots off the user-configured half of the EEPROM. |

| U17 Switch 2 (TST) | OFF: Factory configuration of the EEPROM is protected.           |

| U17 Switch 3 (POS) | OFF: Do not alter this setting.                                  |

| ings |

|------|

| t    |

| Hardware Component  | Default Setting                |

|---------------------|--------------------------------|

| U17 Switch 4 (CT)   | ON: Do not alter this setting. |

| DRAM SIMM Installed | Per customer order             |

Table 1-1.

PCI-MXI-2 Hardware Default Settings (Continued)

| Table 1-2. | PCI-MXI-2 Logical | Address Configuration | Editor Default Settings |

|------------|-------------------|-----------------------|-------------------------|

|            |                   |                       |                         |

| Editor Field                              | Default Setting        |

|-------------------------------------------|------------------------|

| Logical Address                           | 0                      |

| Device Type                               | MBD                    |

| Address Space                             | A16                    |

| VXI Shared RAM Size                       | 0 KB                   |

| Shared RAM Pool                           | 0 KB                   |

| Lower Half Window Byte Swapping           | Disabled (non-swapped) |

| Lower Half Window Memory Select           | System Memory          |

| Upper Half Window Byte Swapping           | Disabled (non-swapped) |

| Upper Half Window Memory Select           | System Memory          |

| Resource Manager Delay                    | 5 s                    |

| Map Upper/Lower Halves to<br>Same Address | Disabled               |

| Editor Field              | Default Setting         |

|---------------------------|-------------------------|

| Default Controller (LA-1) | First Remote Controller |

| System IRQ Level          | 1                       |

| Servant Area Size         | 0                       |

| Number of Handlers        | 1                       |

| Number of Interrupters    | 0                       |

| Protocol Register         | 0xFF0                   |

| Read Protocol Response    | 0x8448                  |

Table 1-3. PCI-MXI-2 Device Configuration Editor Default Settings

Table 1-4. PCI-MXI-2 Bus Configuration Editor Default Settings

| Editor Field                 | Default Setting |

|------------------------------|-----------------|

| MXI System Controller        | Auto            |

| MXI Bus Timeout Value        | 1 ms            |

| MXI CLK10                    | Receive         |

| MXI Transfer Limit           | Unlimited       |

| VXImove uses Synchronous MXI | Enabled         |

| MXI-2 Auto Retry             | Enabled         |

| A24/A32 Write Posting        | Disabled        |

| User Window Size             | 64 KB           |

| Driver Window Size           | 32 KB           |

| Expansion ROM                | Enabled         |

#### VXI/VME-MXI-2

This section summarizes the hardware and software default settings for the VXI-MXI-2 and VME-MXI-2.

| Hardware Component                             | Default Setting                                                                                        |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Logical Address (U43)                          | 1                                                                                                      |

| VXIbus Slot 0/Non-Slot 0 (W2)                  | Automatic detection                                                                                    |

| VXIbus Local Bus (S8, S9)                      | Both OFF: Single VXI-MXI-2                                                                             |

| VXIbus CLK10 Routing (W3)                      | From onboard oscillator                                                                                |

| External Trigger Termination (S2)              | OFF: Unterminated                                                                                      |

| SMB CLK10 Direction (S3)                       | OUT: Drive CLK10 signal                                                                                |

| SMB CLK10 Termination (S4)                     | Ignored; effective only when S3 is set to IN.                                                          |

| Polarity of External SMB CLK10 (S5)            | Inverted                                                                                               |

| MXIbus CLK10 Signal (S7)                       | Receive CLK10 from MXIbus                                                                              |

| MXIbus Termination<br>(U35 switches 1 and 2)   | Automatic MXIbus termination:<br>switch 2 set to YES; switch 1<br>ignored.                             |

| Configuration EEPROM<br>(U35 switches 3 and 4) | User-modifiable; factory settings protected: both switches set to NO.                                  |

| DRAM SIMMs Installed                           | Per customer order                                                                                     |

| SIMM Size Configuration (S6)                   | OFF if SIMMS are $4 \text{ M} \times 32$<br>or larger; ON if smaller than<br>$4 \text{ M} \times 32$ . |

| Table 1-5. | VXI-MXI-2 | Hardware | Default | Settings |

|------------|-----------|----------|---------|----------|

| Table I-J. |           | Tatuwate | Delault | ocumys   |

| Hardware Component                             | Default Setting                                                                                  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------|

| A16 Base Address (U20)                         | Hex C040                                                                                         |

| VME-MXI-2 Intermodule<br>Signaling (W2)        | No user-defined pin selected                                                                     |

| MXIbus Termination<br>(U21 switches 3 and 4)   | Automatic MXIbus termination: switch 3 OFF; switch 4 ignored.                                    |

| Configuration EEPROM<br>(U21 switches 1 and 2) | User-modifiable; factory settings protected: both switches OFF.                                  |

| DRAM SIMMs Installed                           | Per customer order                                                                               |

| SIMM Size Configuration (S2)                   | OFF if SIMMS are $4 \text{ M} \times 32$ or larger; ON if smaller than $4 \text{ M} \times 32$ . |

Table 1-6. VME-MXI-2 Hardware Default Settings

Table 1-7. VXI/VME-MXI-2 Configuration Editor Default Settings

| Editor Field              | Default Setting            |

|---------------------------|----------------------------|

| Logical Address           | 1 (set by hardware switch) |

| LA Selection              | Set by hardware switch     |

| Address Space             | A24 *                      |

| Requested Memory          | 16 KB *                    |

| A16 Write Posting         | Disabled                   |

| A24/A32 Write Posting     | Disabled                   |

| Interlocked Mode          | Disabled                   |

| VXI/VME System Controller | Auto                       |

| VXI/VME Bus Timeout Value | 125 µs                     |

| VXI/VME Auto Retry        | Disabled                   |

| VXI/VME Transfer Limit    | 256                        |

| VXI/VME Arbiter Type      | Priority                   |

| VXI/VME Request Level     | 3                          |

| VXI/VME Fair Request      | Enabled                    |

| Editor Field                                                                         | Default Setting                            |

|--------------------------------------------------------------------------------------|--------------------------------------------|

| VXI/VME Arbiter Timeout                                                              | Enabled                                    |

| MXI System Controller                                                                | Auto                                       |

| MXI Bus Timeout Value                                                                | 1 ms                                       |

| MXI Auto Retry                                                                       | Disabled                                   |

| MXI Transfer Limit                                                                   | Unlimited                                  |

| MXI Parity Checking                                                                  | Enabled                                    |

| MXI Fair Requester                                                                   | Disabled                                   |

| MXI CLK10                                                                            | Set by hardware<br>switch (VXI-MXI-2 only) |

| *Assumes no DRAM is installed. If DRAM is installed, the Address Space would be A32, |                                            |

Table 1-7. VXI/VME-MXI-2 Configuration Editor Default Settings (Continued)

and **Requested Memory** would match the amount of DRAM.

# PCI-MXI-2 Configuration and Installation

This chapter contains the instructions to configure and install the PCI-MXI-2 module.

**Caution** Electrostatic discharge can damage several components on your PCI-MXI-2 module. To avoid such damage in handling the module, touch the antistatic plastic package to a metal part of your computer chassis before removing the PCI-MXI-2 from the package.

# **Configure the PCI-MXI-2**

This section describes how to configure the following options on the PCI-MXI-2:

- Configuration EEPROM

- Onboard DRAM

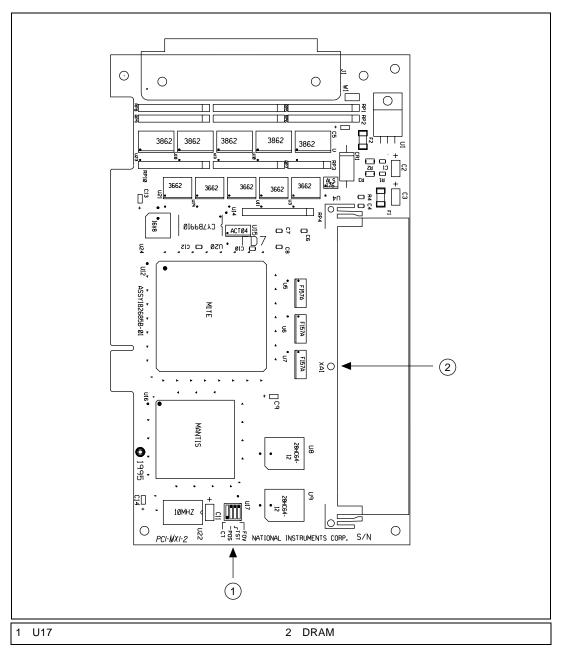

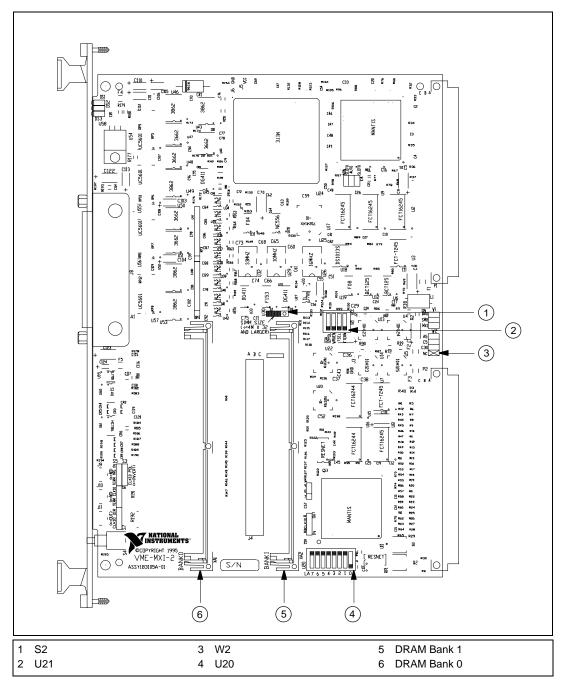

Figure 2-1 shows the PCI-MXI-2. The drawing shows the location and factory-default settings on the module.

Figure 2-1. PCI-MXI-2 Parts Locator Diagram

#### **Configuration EEPROM**

The PCI-MXI-2 has an onboard EEPROM, which stores default register values that are loaded at power-on. The EEPROM is divided into two halves—a factory-configuration half, and a user-configuration half—so you can modify the user-configurable half, while the factory-configured half stores a back-up of the default user settings. The factory configuration is a minimal configuration that allows you to boot your PCI-MXI-2 regardless of the changes made to the user configuration.

For information on configuring the onboard EEPROM, refer to Appendix C, *EEPROM Configuration*.

### **Onboard DRAM**

The PCI-MXI-2 can accommodate one DRAM SIMM. Table 2-1 lists the SIMMs you can use. You can use 32-bit or 36-bit SIMMs because DRAM parity is not required. The PCI-MXI-2 can hold up to 16 MB of onboard memory. The PCI-MXI-2 supports DRAM speeds of 80 ns or faster. The maximum DRAM SIMM size is 1 in.

| SIMMs                       | Total DRAM | National Instruments<br>Option? |

|-----------------------------|------------|---------------------------------|

| —                           | 0          | _                               |

| 256 K × 32 or<br>256 K × 36 | 1 MB       | _                               |

| 1 M × 32 or<br>1 M × 36     | 4 MB       | YES                             |

| 4 M × 32 or<br>4 M × 36     | 16 MB      | YES                             |

Table 2-1. PCI-MXI-2 DRAM Configurations

# Install the PCI-MXI-2

This section contains general installation instructions for the PCI-MXI-2. Consult your computer user manual or technical reference manual for specific instructions and warnings.

1. Plug in your PCI-based computer before installing the PCI-MXI-2. The power cord grounds the computer and protects it from electrical damage while you are installing the module.

**Warning** To protect both yourself and the computer from electrical hazards, the computer should remain off until you are finished installing the PCI-MXI-2 module.

- 2. Remove the top cover or access port to the PCI bus.

- 3. Select any available PCI expansion slot.

- 4. Touch the metal part of the power supply case inside the computer to discharge any static electricity that might be on your clothes or body.

- 5. Line up the PCI-MXI-2 with the MXI-2 connector near the cut-out on the back panel. Slowly push down on the top of the PCI-MXI-2 until its card-edge connector is resting on the expansion slot receptacle. Using slow, evenly distributed pressure, press the PCI-MXI-2 straight down until it seats in the expansion slot.

- 6. Check the installation. Ensure that the PCI-MXI-2 is secure in its slot.

- 7. Replace the computer cover.

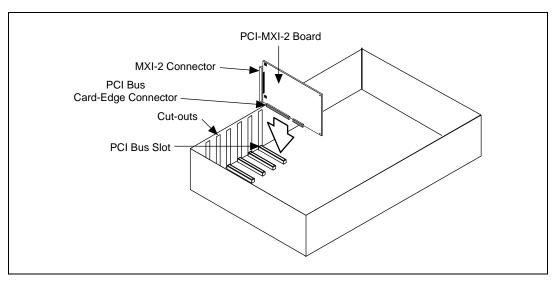

Figure 2-2 shows how to install the PCI-MXI-2.

Figure 2-2. PCI-MXI-2 Installed in a Computer

# 3

# VXI-MXI-2 Configuration and Installation

This chapter contains the instructions to configure and install the VXI-MXI-2 module. This chapter applies only if you ordered the VXI-PCI8026 interface kit. If you ordered the VME-PCI8026 kit, skip this chapter and refer to Chapter 4, *VME-MXI-2 Configuration and Installation*.

**Caution** Electrostatic discharge can damage several components on your VXI-MXI-2 module. To avoid such damage in handling the module, touch the antistatic plastic package to a metal part of your VXI chassis before removing the VXI-MXI-2 from the package.

# **Configure the VXI-MXI-2**

This section describes how to configure the following options on the VXI-MXI-2:

- VXIbus logical address

- VXIbus Slot 0/Non-Slot 0

- VXIbus local bus

- VXIbus CLK10 routing

- Trigger input termination

- MXIbus termination

- Configuration EEPROM

- Onboard DRAM

**Note** If you have only one VXI chassis in your system, you should leave the VXI-MXI-2 at Logical Address 1 and install it into Slot 0. To install the VXI-MXI-2, see *Install the VXI-MXI-2* later in this chapter.

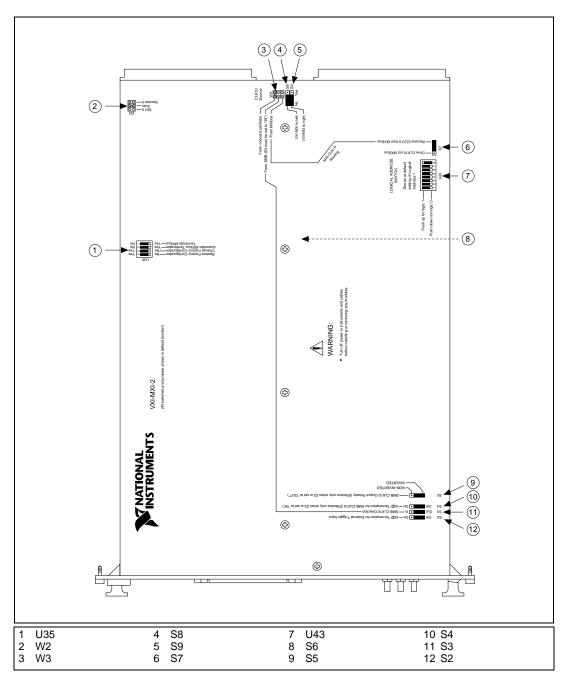

Figure 3-1 shows the VXI-MXI-2 as it would appear when facing the right side cover. The drawing shows the location and factory-default settings of most of the configuration switches and jumpers on the module. Notice that switch S6 is accessible only by removing the front cover.

Figure 3-1. VXI-MXI-2 Right-Side Cover

#### **Front Panel Features**

The VXI-MXI-2 has the following front panel features:

- Three front panel LEDs

- SYSFAIL LED indicates that the VMEbus SYSFAIL line is asserted.

- MXI LED indicates when the VXI-MXI-2 is accessed from the MXIbus.

- VXI LED indicates when the VXI-MXI-2 is accessed from the VXIbus.

- MXIbus connector

- Three SMB connectors

- External clock

- Trigger output

- Trigger input

- System reset push-button

#### **Removing the Metal Enclosure**

The VXI-MXI-2 is housed in a metal enclosure to improve EMC performance and to provide easy handling. Because the enclosure includes cutouts to facilitate changes to the switch and jumper settings, it should not be necessary to remove it under normal circumstances.

However, it is necessary to remove the enclosure if you want to change the amount of DRAM installed on the VXI-MXI-2. Switch S6, which is directly related to the amount of DRAM you want to install, is also accessible only by removing the enclosure. If you will be making this change, remove the four screws on the top, the four screws on the bottom, and the five screws on the right side cover of the enclosure. Refer to the *Onboard DRAM* section later in this chapter for details about changing DRAM.

#### **VXIbus Logical Address**

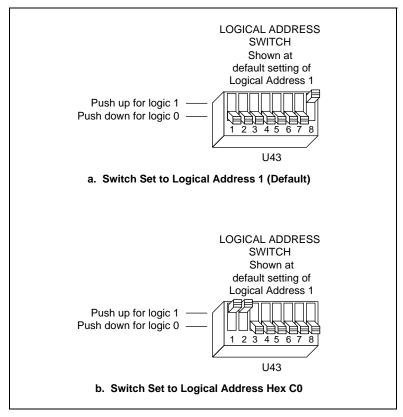

Each device in a VXIbus/MXIbus system is assigned a unique number between 0 and 254. This 8-bit number, called the *logical address*, defines the base address for the VXI configuration registers located on the device. With unique logical addresses, each VXIbus device in the system is assigned 64 bytes of configuration space in the upper 16 KB of A16 space. Logical address 0 is reserved for the Resource Manager in the VXIbus system. Because the VXI-MXI-2 cannot act as a Resource Manager, do not configure the VXI-MXI-2 with a logical address of 0.

Some VXIbus devices have *dynamically configurable* logical addresses. These devices have an initial logical address of hex FF or 255, which indicates that they can be dynamically configured. While the VXI-MXI-2 does support dynamic configuration of VXI devices within its mainframe, it is itself a *statically configured* device and is preset at the factory with a VXI logical address of 1.

Ensure that no other statically configurable VXIbus devices have a logicaladdress of 1. If they do, change the logical address setting of either the VXI-MXI-2 or the other device so that every device in the system has a unique associated logical address.

You can change the logical address of the VXI-MXI-2 by changing the setting of the 8-bit DIP switch labeled *LOGICAL ADDRESS SWITCH* (location designator U43) on the panel. The down position of the DIP switch corresponds to a logic value of 0 and the up position corresponds to a logic value of 1. Verify that the VXI-MXI-2 does not have the same logical address as any other statically configured VXIbus device in your system. Remember that logical addresses hex 0 and FF are not allowed for the VXI-MXI-2. Also, when setting logical addresses, keep in mind the grouping requirements set by the system hierarchy. See VXI-6, *VXIbus Mainframe Extender Specification*, for more information on setting logical addresses on a multimainframe hierarchy.

Figure 3-2 shows switch settings for logical address hex 1 and C0.

Figure 3-2. Logical Address Selection

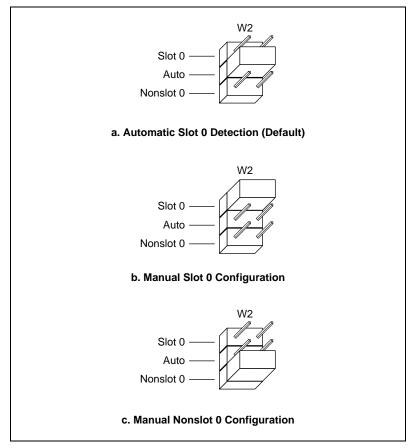

# VXIbus Slot O/Non-Slot O

The VXI-MXI-2 is configured at the factory to automatically detect if it is installed in Slot 0 of a VXIbus mainframe. With automatic Slot 0 detection, you can install the VXI-MXI-2 into any VXIbus slot.

You can manually configure the VXI-MXI-2 for either Slot 0 or Non-Slot 0 operation by defeating the automatic-detection circuitry. Use the three-position jumper W2 to select automatic Slot 0 detection, Slot 0, or Non-Slot 0 operation. Figure 3-3 shows these three settings.

**Caution** Do not install a device configured for Slot 0 into another slot without first reconfiguring it to either Non-Slot 0 or automatic configuration. Neglecting to do this could damage the device, the VXIbus backplane, or both.

Figure 3-3. VXIbus Slot Configuration

When the VXI-MXI-2 is installed in Slot 0, it becomes the VMEbus System Controller. In this role, it has VMEbus Data Transfer Bus Arbiter circuitry that accepts bus requests on all four VMEbus request levels, prioritizes the requests, and grants the bus to the highest priority requester. As VMEbus System Controller, the VXI-MXI-2 also drives the 16 MHz VMEbus system clock by an onboard 16 MHz oscillator.

As required by the VXIbus specification, the VXI-MXI-2 drives the 10 MHz signal CLK10 on a differential ECL output when installed in Slot 0. When not installed in Slot 0, the VXI-MXI-2 only receives the CLK10 signal.

#### **VXIbus Local Bus**

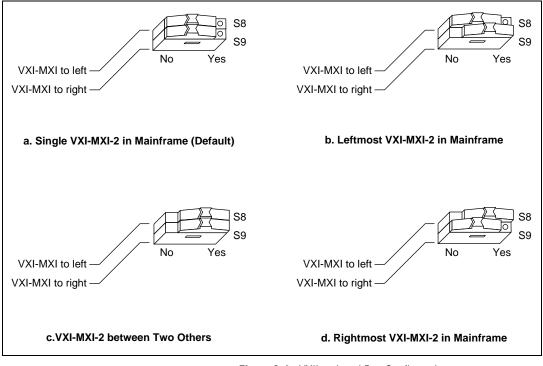

If you will be installing more than one VXI-MXI-2 in a single VXIbus mainframe, you must configure the boards to use the local bus. The VXI-MXI-2 uses the local bus to pass a signal to the other VXI-MXI-2 modules in the mainframe to disable the VMEbus bus timeout unit (BTO) during cycles that map to the MXIbus. Because the local bus is used, you need to install all VXI-MXI-2 modules for a single mainframe in adjacent slots.

You will use two switches on the VXI-MXI-2 to select its position in relation to any other VXI-MXI-2 module in the mainframe. Use switch S9 when there is a VXI-MXI-2 to the right (higher numbered slot). Use S8 when there is a VXI-MXI-2 to the left (lower numbered slot).

Figure 3-4 shows four configuration settings for a VXI-MXI-2. Figure 3-4a illustrates the default setting, which is for a single VXI-MXI-2 in a mainframe. Use the setting in Figure 3-4b for the VXI-MXI-2 located to the left of all others. Figure 3-4c shows the setting to use if the VXI-MXI-2 is between two others. Use the setting of Figure 3-4d for the VXI-MXI-2 located to the right of all others.

Figure 3-4. VXIbus Local Bus Configuration

# **VXIbus CLK10 Routing**

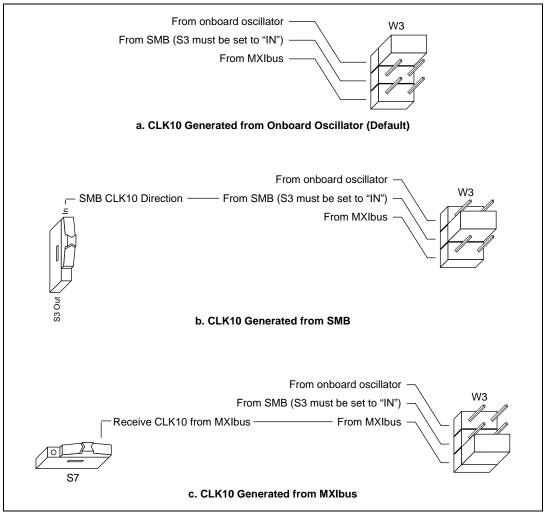

When the VXI-MXI-2 is installed in Slot 0 of your mainframe, it supplies the VXIbus CLK10 signal. The VXI-MXI-2 can use three different sources to generate this signal: an onboard oscillator, the external CLK SMB connector, and the MXIbus CLK10 signal. Use the three-position jumper W3 to select these options, as shown in Figure 3-5.

Notice that Figure 3-5b and Figure 3-5c also show switches S3 and S7, respectively. You must configure these switches as shown when using the corresponding CLK10 source setting of W3.

Figure 3-5. VXIbus CLK10 Routing

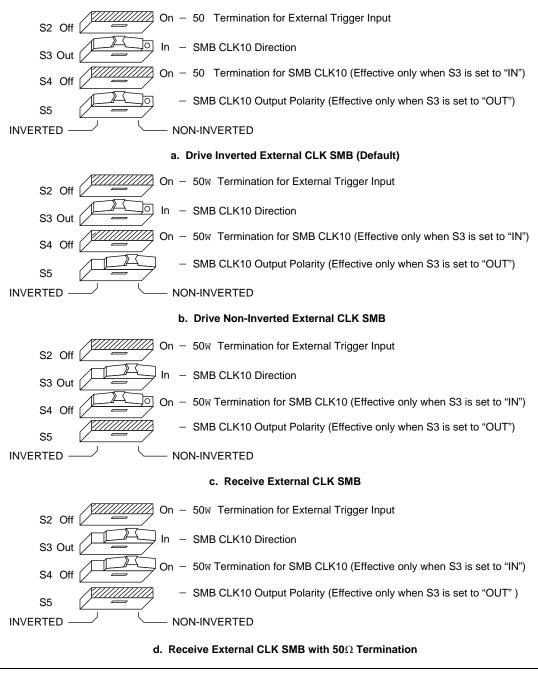

The VXI-MXI-2 can also be configured to drive the external CLK SMB signal from the VXIbus CLK10 signal. Switch S3 controls whether the VXI-MXI-2 drives or receives the external CLK SMB signal. If you change the S3 setting to drive CLK10 out the external CLK10 SMB connector, do not set the W3 jumper to receive the SMB CLK10 signal; instead use the settings shown in either Figure 3-5a or Figure 3-5c as appropriate.

When switch S3 is set so that the VXI-MXI-2 receives the SMB CLK10 signal, you have the option to add a 50 is unused—its setting does not matter—when S3 is configured to drive the external CLK SMB signal.

You can use an additional switch, S5, to control the polarity of the external CLK SMB signal when S3 is configured to drive it. S5 is unused—its setting does not matter—when S3 is configured to receive the external CLK SMB signal.

Figure 3-6 shows four configuration settings for the VXI-MXI-2. Figure 3-6a shows the default configuration, which is for driving the inverted external CLK SMB. Use the settings of Figure 3-6b to drive the noninverted external CLK SMB signal. Figure 3-6c illustrates the setting for receiving the external CLK SMB signal. Finally, you can configure the switches as shown in Figure 3-6d to receive the external CLK SMB signal with a 50  $\Omega$  termination.

**Note** The settings of any switches shown with this pattern ( $\square$ ) have no bearing on the configuration described in any of the following figures.

Figure 3-6. SMB CLK10 Settings

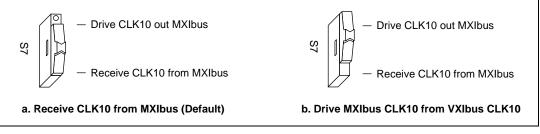

The VXI-MXI-2 can also drive or receive the MXIbus CLK10 signal. Switch S7 controls whether the VXI-MXI-2 drives MXIbus CLK10 from the VXIbus CLK10 or receives MXIbus CLK10. As shown earlier in Figure 3-5c, if W3 is configured to use the MXIbus CLK10 to generate the VXIbus CLK10 signal, switch S7 must be configured to receive MXIbus CLK10. This is shown again in Figure 3-7a below. If you change the S7 setting to drive CLK10 out the MXIbus, do not set the W3 jumper to receive the MXIbus CLK10; instead use the settings shown in Figure 3-5a or Figure 3-5b as appropriate.

$\triangle$

**Caution** Do not configure more than one MXIbus device to drive the MXIbus CLK10. Having a second device driving MXIbus CLK10 could damage the device.

Figure 3-7 shows the configuration settings for receiving and driving MXIbus CLK10, respectively.

Figure 3-7. Receiving or Driving MXIbus CLK10

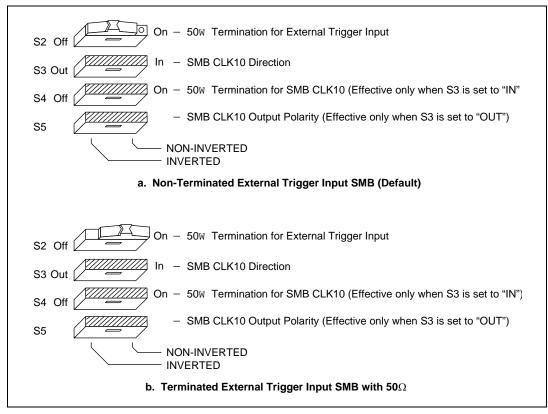

# **Trigger Input Termination**

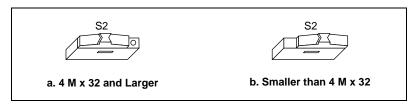

You can use switch S2 to terminate the external trigger input SMB with 50  $\Omega$ . Figure 3-8a shows the default setting for a nonterminated trigger input SMB. Use the setting of Figure 3-8b to terminate the trigger input SMB. Switch S2 is located above switches S3, S4, and S5, which have no effect on this configuration.

Figure 3-8. SMB Trigger Input Termination

#### **MXIbus Termination**

The first and last MXIbus devices connected to the MXIbus—whether it is a single MXI-2 cable or daisy-chained MXI-2 cables—must terminate the MXIbus. Any MXIbus devices in the middle of a MXIbus daisy chain must *not* terminate the MXIbus.

The VXI-MXI-2 automatically senses whether it is at either end of the MXIbus cable to terminate the MXIbus. You can manually control MXIbus termination by defeating the automatic circuitry. Use switches 1 and 2 of the four-position switch at location U35 to control whether MXIbus termination is automatic (Figure 3-9a), on (Figure 3-9b), or off (Figure 3-9c). The settings of switches 3 and 4 have no effect on MXIbus termination.

Use switch 2 of U35 to select whether you want the VXI-MXI-2 to automatically control termination of the MXIbus. Switch 1 of U35 lets you manually control whether to terminate the MXIbus when automatic termination is turned off. Switch 1 has no effect when switch 2 is set for automatic MXIbus termination; you must turn off automatic termination if you want to manually control termination.

Figure 3-9. MXIbus Termination

# **Configuration EEPROM**

The VXI-MXI-2 has an onboard EEPROM, which stores default register values that are loaded at power-on. The EEPROM is divided into two halves—a factory-configuration half, and a user-configuration half. Both halves were factory configured with the same configuration values so you can modify the user-configurable half, while the factory-configured half stores a back-up of the default user settings.

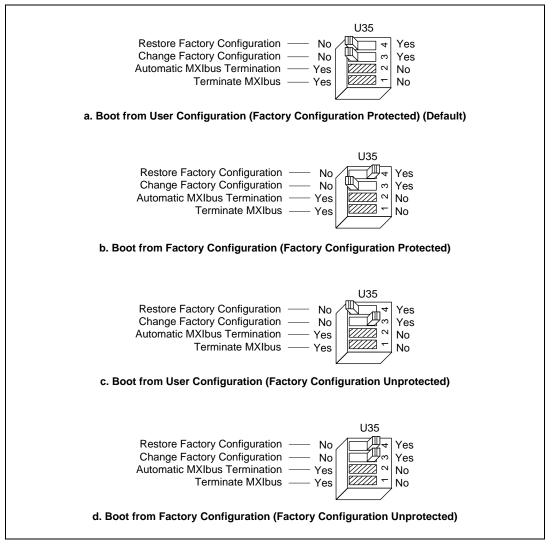

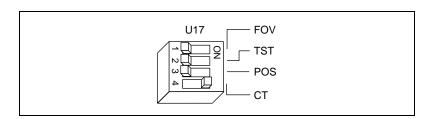

Use switches 3 and 4 of the four-position switch at location U35 to control the operation of the EEPROM. The Restore Factory Configuration switch (switch 4) causes the VXI-MXI-2 to boot off the factory-configured half instead of the user-modified settings. This is useful in the event that the user-configured half of the EEPROM becomes corrupted in such a way that the VXI-MXI-2 boots to an unusable state.

The Change Factory Configuration switch (switch 3 of U35) lets you change the factory-default configuration settings by permitting writes to the factory settings section of the EEPROM. This switch serves as a safety measure and should not be needed under normal circumstances. When this switch is off (its default setting) the factory configuration of the EEPROM is protected, so any writes to the factory area will be ignored. The factory area is protected regardless of the setting of switch 4 of U35.

Figure 3-10 shows the configuration settings for EEPROM operation. The settings of switches 1 and 2 have no effect on EEPROM configuration.

Figure 3-10. EEPROM Operation

# **Onboard DRAM**

The VXI-MXI-2 can accommodate up to two 1.35 in. DRAM SIMMs. Table 3-1 lists the SIMMs you can use.

| Bank 0                                   | Bank 1                      | Total DRAM | National<br>Instruments<br>Option? | Switch Setting<br>of S6 |

|------------------------------------------|-----------------------------|------------|------------------------------------|-------------------------|

|                                          | —                           | 0          | _                                  | _                       |

| 256 K × 32 or<br>256 K × 36              | —                           | 1 MB       | _                                  | ON                      |

| 256 K × 32 or<br>256 K × 36              | 256 K × 32 or<br>256 K × 36 | 2 MB       | _                                  | ON                      |

| 512 K × 32 or<br>512 K × 36              | —                           | 2 MB       | _                                  | ON                      |

| 512 K × 32 or<br>512 K × 36              | 512 K × 32 or<br>512 K × 36 | 4 MB       | _                                  | ON                      |

| 1 M × 32 or<br>1 M × 36                  |                             | 4 MB       | YES                                | ON                      |

| 1 M × 32 or<br>1 M × 36                  | 1 M × 32 or<br>1 M × 36     | 8 MB       | _                                  | ON                      |

| $2 M \times 32 \text{ or} 2 M \times 36$ | —                           | 8 MB       | YES                                | ON                      |

| 2 M × 32 or<br>2 M × 36                  | 2 M × 32 or<br>2 M × 36     | 16 MB      | _                                  | ON                      |

| 4 M × 32 or<br>4 M × 36                  | —                           | 16 MB      | YES                                | OFF                     |

| 4 M × 32 or<br>4 M × 36                  | 4 M × 32 or<br>4 M × 36     | 32 MB      | —                                  | OFF                     |

| 8 M × 32 or<br>8 M × 36                  | —                           | 32 MB      | YES                                | OFF                     |

| 8 M × 32 or<br>8 M × 36                  | 8 M × 32 or<br>8 M × 36     | 64 MB      | YES                                | OFF                     |

Table 3-1. VXI-MXI-2 DRAM Configurations

You can use 32-bit or 36-bit SIMMs because DRAM parity is not required. Because the VXI-MXI-2 supports only one organization at a time, all SIMMs installed must be of the same type. Use Bank 0 first when installing the SIMMs. This allows you to install up to 64 MB. The VXI-MXI-2 supports DRAM speeds of 80 ns or faster.

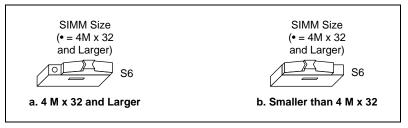

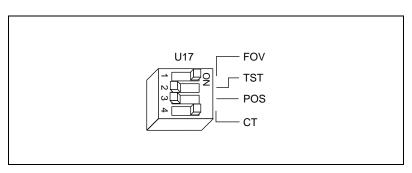

Switch S6 is used to select the size of each SIMM. The SIMM sockets and S6 are accessible only by removing the right-side cover. To access these components, remove the four screws on the top, the four screws on the bottom, and the five screws on the right-side cover of the metal enclosure. If the SIMMs are  $4 \text{ M} \times 32$  or larger, S6 should be in the OFF setting as shown in Figure 3-11a. For SIMMs *smaller* than  $4 \text{ M} \times 32$ , use the ON setting as shown in Figure 3-11b.

Figure 3-11. SIMM Size Configuration

Refer to Table 3-1 for how to adjust the switch (ON or OFF) for all supported DRAM configurations. Many of the DRAM options are available from National Instruments.

# Install the VXI-MXI-2

This section contains general installation instructions for the VXI-MXI-2. Consult your VXIbus mainframe user manual or technical reference manual for specific instructions and warnings.

1. Plug in your mainframe before installing the VXI-MXI-2. The power cord grounds the mainframe and protects it from electrical damage while you are installing the module.

**Warning** To protect both yourself and the mainframe from electrical hazards, the mainframe should remain off until you are finished installing the VXI-MXI-2 module.

2. Remove or open any doors or covers blocking access to the mainframe slots.

If you are installing the VXI-MXI-2 into a D-size mainframe, install a support designed for installing C-size boards in D-size mainframes. The VXI-MXI-2 has no P3 connector and cannot provide P3 Slot 0 control to VXI devices requiring this capability.

**Caution** If the VXI-MXI-2 is not configured for automatic Slot 0 detection, be certain that the slot you select in your VXIbus mainframe matches the VXI-MXI-2 configuration as either a Slot 0 device or a Non-Slot 0 device. If you install your VXI-MXI-2 into a slot that does not correspond with the jumper setting, you risk damage to the VXI-MXI-2, the VXIbus backplane, or both.

- 4. Insert the VXI-MXI-2 in the slot you have selected by aligning the top and bottom of the board with the card-edge guides inside the mainframe. Slowly push the VXI-MXI-2 straight into the slot until its plug connectors are resting on the backplane receptacle connectors. Using slow, evenly distributed pressure, press the VXI-MXI-2 straight in until it seats in the expansion slot. The front panel of the VXI-MXI-2 should be even with the front panel of the mainframe.

- 5. Tighten the retaining screws on the top and bottom edges of the front panel.

- 6. Check the installation.

- 7. Connect the cables as described in the following section before restoring power.

- 8. Replace or close any doors or covers to the mainframe.

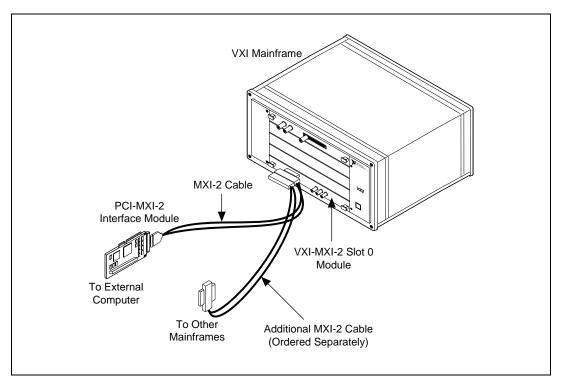

# **Connect the MXIbus Cable**